XMSRC4192-VC1¶

2通道192KHz ASRC音频采样率转换器集成2路S/PDIF和2路I2S接口

1、简介¶

1.1 产品描述¶

XMSRC4192是一款基于XMOS芯片架构的高性能2通道异步采样率转换器,提供16:1至1:16的宽范围采样率转换、144dB动态范围以及对I2S、Left-justified、Right-justified等多种数字音频格式的全面支持。

- 该产品集成了两个S/PDIF输入接口,为用户提供更灵活的信号源选择。用户可根据应用需求在I2S输入和S/PDIF输入之间灵活切换,显著增强了系统的连接性和适应性。

- XMOS芯片架构确保了产品的高可靠性和出色的音频处理性能,为专业音频设备制造商提供了更具竞争力的解决方案选择。

- 单SRC模块架构,可同时处理2通道音频采样率转换。

1.2 产品特性¶

-

双通道SRC音频采样率转换

- 单SRC模块架构

- 处理2路音频信号(立体声)

- 可配置输入源

- 同时处理2通道音频采样率转换

- 灵活的信号路由

- 输入可选: I2S_IN 或 S/PDIF_I

- 输出可选:I2S_OUT 或 S/PDIF_O

- 支持多种工作模式

- 单SRC模块架构

-

超高采样率转换支持

- ASRC (异步采样率转换)

- 支持44.1KHz-192KHz间采样率转换

- 支持16:1至1:16宽范围输入输出采样率比

- 自动感应输入输出采样率

- 音频数据处理

- 支持16bit/24bit/32bit音频数据处理

- 144dB动态范围

- THD+N: -140dB

- ASRC (异步采样率转换)

-

多接口支持

- S/PDIF接口

- 2个S/PDIF输入输出接口(S/PDIF_I, S/PDIF_O)

- 兼容AES3, IEC 60958, and EIAJ CP-1201标准

- I²S接口

- 2个I²S接口(1个输入 + 1个输出)

- 支持Master/Slave模式

- S/PDIF接口

-

全面的数字音频格式支持

- 支持I2S, Left-Justified, Right-Justified格式

- 支持16bit/24bit/32bit音频数据处理

- 所有输出数据从内部28位数据路径抖动处理

-

灵活配置接口

- I²C/UART配置接口

- 支持I²C和UART双协议配置

- 可配置参数

- 输入输出模式

- I²S采样率配置(Master模式)

- Master/Slave模式切换

- I²S音频格式(I²S/Left-Justified/Right-Justified)

- I²C/UART配置接口

-

智能时钟管理

- 主时钟输出(MCLK)

- 支持128fs、256fs、512fs、1024fs参考时钟

- 主时钟输出(MCLK)

1.3 应用场景¶

-

专业录音棚

- 立体声录音设备中进行高精度采样率转换

- 音频工作站中处理不同采样率的音频素材

- 调音台系统中实现音频信号格式统一

-

广播电视

- 广播设备中音频信号的实时处理

- 电视制作中不同来源音频的同步处理

- 直播系统中音频信号的优化转换

-

数字音响

- 功放设备中音频信号的预处理

- 音频处理器中立体声信号转换

- 扬声器管理系统中信号优化

-

汽车音响

- 车载娱乐系统中音频格式转换

- 高端音响中音质优化处理

- 降噪系统中信号处理

-

消费电子

- 高端音响设备中音频信号处理

- 家庭影院系统中立体声处理

- 专业音频接口中信号转换

-

工业应用

- 音频测试设备中信号标准化

- 音频分析仪器中数据处理

- 专业信号处理设备中格式转换

1.4 产品功能框图¶

1.5 订购信息¶

| PRODUCT MODEL | ORDERING NUMBER | PACKAGE BODY | SIZE (NOM) | Hardware Model | Comments |

|---|---|---|---|---|---|

| XMSRC4192-VC1 | XMSRC4192-VC1 | SMT LGA-52 | 13x13mm | A316-Mini-V1 | 2通道192KHz ASRC采样率转换器,单SRC模块,2路S/PDIF输入 |

2、模式及指标¶

2.1 支持的输入输出模式¶

XMSRC4192-VC1采用单SRC模块设计,可配置不同的输入源,以下列出典型应用模式:

| 模式编号 | 输入输出模式 | 说明 |

|---|---|---|

| 1 | S/PDIF_I → SRC → I²S_OUT (Master) | S/PDIF_I转I²S输出 |

| 2 | S/PDIF_I → SRC → I²S_OUT (Slave) | S/PDIF_I转I²S输出 |

| 3 | I²S_IN (Master) → SRC → S/PDIF_O | I²S输出转S/PDIF_O输出 |

| 4 | I²S_IN (Slave) → SRC → S/PDIF_O | I²S输出转S/PDIF_O输出 |

| 5 | I²S_IN (Master) → SRC → I²S_OUT (Master) | 立体声采样率转换 |

| 6 | I²S_IN (Slave) → SRC → I²S_OUT (Master) | 立体声采样率转换 |

| 7 | S/PDIF_I → SRC → S/PDIF_O | S/PDIF_I转S/PDIF_O输出 |

模式配置说明

- 配置通过I²C/UART接口动态切换

2.2 音频性能指标¶

| 性能指标 | ASRC模式 | 测试条件 |

|---|---|---|

| 分辨率 | 16-32位 | - |

| 输入采样频率 | 44.1kHz ~ 192kHz | - |

| 输出采样频率 | 44.1kHz ~ 192kHz | - |

| 动态范围 | 144dB | -60dBFS输入, A-weighted |

| THD+N | -140dB | 0dBFS输入, 20Hz~fs/2 |

3、管脚配置和功能¶

3.1 XMSRC4192_VC1管脚布局¶

3.2 XMSRC4192_VC1管脚描述¶

| 管脚序号 | 名称 | 类型 | 功能 |

|---|---|---|---|

| 1 | 3.3V | P | 模组3.3V供电 |

| 2 | X1D13 | I | S/PDIF_B (S/PDIF输出) |

| 3 | X1D16 | - | 保留 |

| 4 | GND | P | 模组地 |

| 5 | X1D17 | - | 保留 |

| 6 | X1D18 | - | 保留 |

| 7 | X1D19 | - | 保留 |

| 8 | X1D22 | - | 保留 |

| 9 | X0D29 | I/O | NC |

| 10 | X0D35 | I/O | BCLKI (I²S输入位时钟, Master输出/Slave输入) |

| 11 | X0D36 | I/O | LRCKI (I²S输入帧同步, Master输出/Slave输入) |

| 12 | X0D37 | I | S/PDIF_I(S/PDIF输入) |

| 13 | X0D38 | - | SDIN (I²S数据输入) |

| 14 | X0D40 | I/O | NC |

| 15 | X0D39 | O | MCLK_OUT (主时钟输出) |

| 16 | X0D42 | - | 保留 |

| 17 | X0D41 | I/O | NC |

| 18 | X0D43 | - | 保留 |

| 19 | X1D34 | - | 保留 |

| 20 | GND | P | 模组地 |

| 21 | X0D30 | I/O | CTL_MUTE |

| 22 | X0D31 | I/O | UART_I2C_SEL (UART/I2C选择) |

| 23 | X0D32 | I/O | NC |

| 24 | X0D33 | - | 保留 |

| 25 | GND | P | 模组地 |

| 26 | GND | P | 模组地 |

| 27 | GND | P | 模组地 |

| 28 | X0D00 | I | UART_TX/I2C_SCL |

| 29 | X0D11 | O | UART_RX/I2C_SDA |

| 30 | X1D00 | - | LRCKO (I²S输出帧同步, Master输出/Slave输入) |

| 31 | X1D01 | - | SDOUT (I²S数据输出) |

| 32 | GND | P | 模组地 |

| 33 | X1D09 | - | 保留 |

| 34 | X1D10 | - | BCLKO (I²S输出位时钟, Master输出/Slave输入) |

| 35 | X1D11 | O | MCLK_OUT (主时钟输出) |

| 36 | GND | P | 模组地 |

| 37 | GND | P | 模组地 |

| 38 | TDI | I/O | JTAG调试接口 |

| 39 | TDO | I/O | JTAG调试接口 |

| 40 | TMS | I/O | JTAG调试接口 |

| 41 | TCK | I/O | JTAG调试接口 |

| 42 | RST_N | I | 系统复位,低电平有效 |

| 43 | 1.8V | P | 模组1.8V供电 |

| 44 | GND | P | 模组地 |

| 45 | USB_DM | I/O | USB_DM (保留,未使用) |

| 46 | USB_DP | I/O | USB_DP (保留,未使用) |

| 47 | GND | P | 模组地 |

| 48 | 0.9V | P | 模组0.9V供电 |

| 49 | GND | P | 模组地 |

| 50 | GND | P | 模组地 |

| 51 | GND | P | 模组地 |

| 52 | GND | P | 模组地 |

管脚类型说明

表中I/O类型定义:I=输入,O=输出,P=电源,I/O=输入/输出

重要说明

- UART/I2C接口选择: 通过管脚22(X0D31)的UART_I2C_SEL信号选择接口类型

- MCLK输出: 管脚15(X0D39)和管脚35(X1D11)

- Master模式需要,支持128fs/256fs/512fs/1024fs

4、配置接口说明¶

4.1 I²C/UART配置接口¶

XMSRC4192-VC1支持I²C和UART双协议配置,提供灵活的配置方式。通过管脚22(X0D31)的UART_I2C_SEL信号可以选择使用哪种配置接口:

| 配置方式 | 管脚22(X0D31) | 通信接口 | 说明 |

|---|---|---|---|

| 上拉 | UART_I2C_SEL | UART模式 | 管脚29(X0D11)=UART_RX, 管脚28(X0D01)=UART_TX |

| 下拉 | UART_I2C_SEL | I²C模式 | 管脚29(X0D11)=I2C_SDA, 管脚28(X0D01)=I2C_SCL |

4.2 可配置参数¶

通过I²C或UART接口可配置以下参数:

| 参数类型 | 配置选项 | 说明 |

|---|---|---|

| 输入输入模式 | 输入输出模式7选一 | |

| I²S采样率 | 4kHz~192kHz | Master模式下配置 |

| I²S输入格式 | I²S/Left-Justified/Right-Justified | 音频数据格式 |

| I²S输出格式 | I²S/Left-Justified/Right-Justified | 音频数据格式 |

| 输出字长 | 16/24/32位 |

配置说明

- 详细配置命令请参考配置协议文档

4.3 MCLK配置¶

- Master模式端口需要MCLK,用于生成LRCK和BCK

- MCLK支持128fs/256fs/512fs/1024fs

5、硬件参数¶

5.1、正常工作条件¶

| 功能 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|

| 工作温度 | 0 | - | 70 | ℃ |

| 3.3V工作电压 | 3.0 | 3.3 | 3.6 | V |

| 1.8V工作电压 | 1.62 | 1.80 | 1.98 | V |

| 0.9V工作电压 | 0.855 | 0.90 | 0.945 | V |

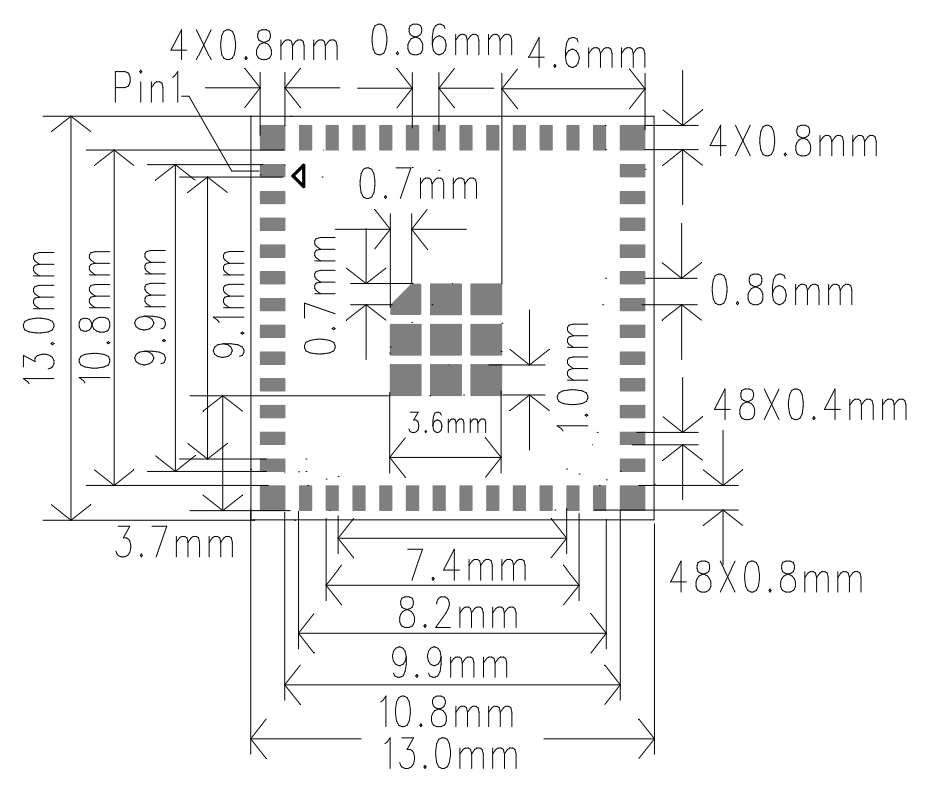

5.2 产品尺寸¶

13±0.1mm(L)X13±0.1mm(W)X0.8±0.1mm(H)

5.3 模组封装图¶

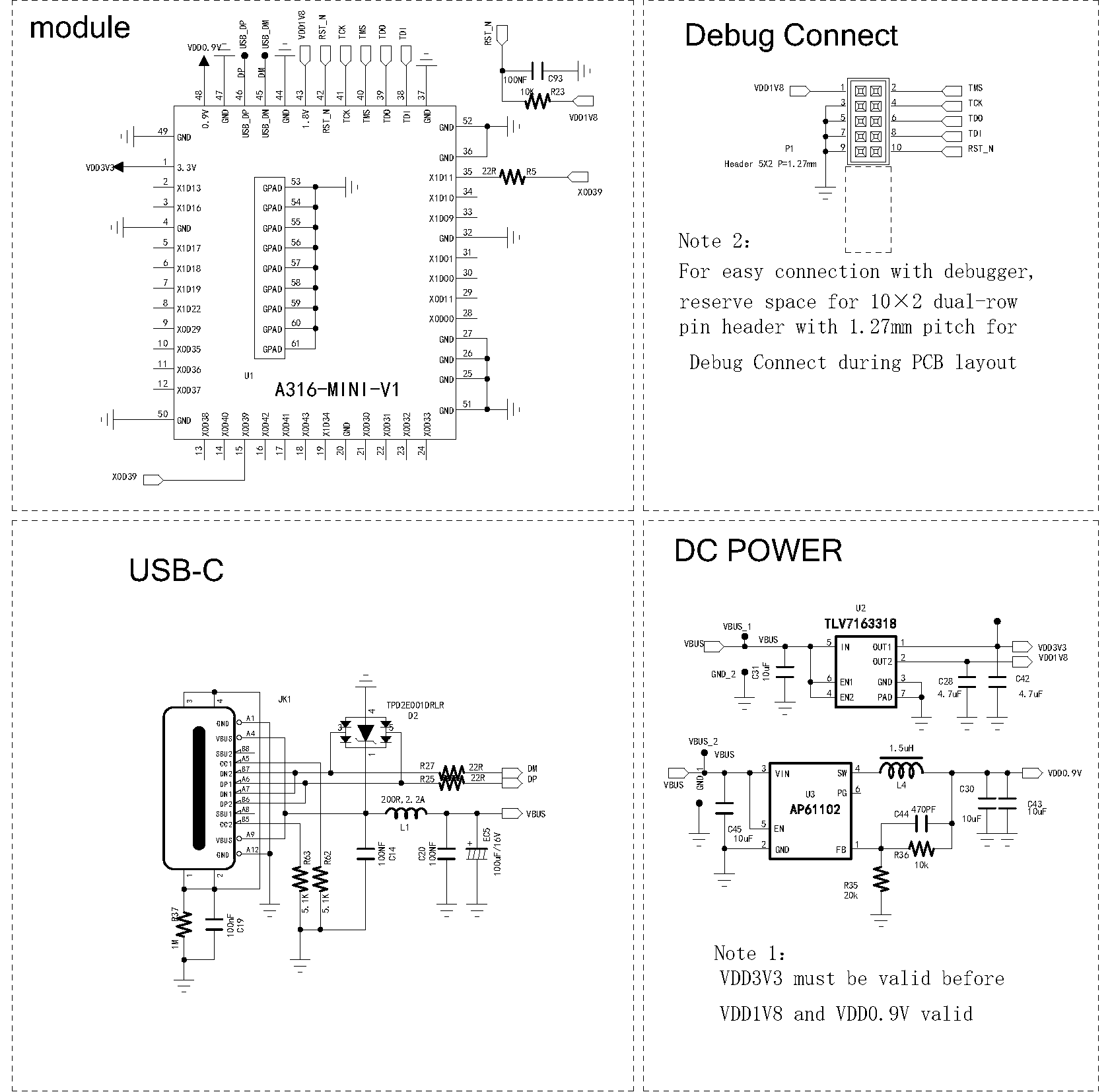

6、最小系统参考设计¶

7、产品包装信息¶

托盘+外箱包装

8、修订历史¶

| 版本 | 日期 | 描述 | 修订者 |

|---|---|---|---|

| V1.0 | 2025-10-6 | 初始版本发布 | 技术文档部 |