XMSRC4392-VC1¶

4-Channel 192KHz ASRC and 768KHz SSRC Audio Sample Rate Converter with Integrated S/PDIF Transceiver and Dual I2S Master/Slave Interfaces

1. Introduction¶

1.1 Product Description¶

XMSRC4392 is a high-performance 4-channel asynchronous audio sample rate converter based on XMOS high-performance chips, designed specifically for professional audio applications. Compared to the SRC4392's dual-channel SRC solution, this product provides double the processing capability while achieving significant optimization in both cost and performance.

- The product integrates two independent SRC modules (SRC_A and SRC_B), each capable of processing two audio channels, supporting ultra-high sample rates up to 768KHz, providing exceptional flexibility and high-performance audio sample rate conversion for various digital audio systems.

- Supports SSRC with sample rate conversion from 44.1KHz to 768KHz, ASRC with sample rate conversion from 44.1KHz to 192KHz, and supports 16-bit/24-bit/32-bit audio data processing.

- The product features excellent audio performance specifications, with THD+N (@1kHz, 0dBFs) ≤ -130dB for both SSRC and ASRC, providing professional-grade audio processing solutions for audio equipment manufacturers.

1.2 Product Features¶

-

Four-Channel SRC Audio Sample Rate Conversion

- Dual SRC Module Architecture (SRC_A + SRC_B)

- Each module processes 2 audio channels

- Independently configurable input sources

- Total simultaneous processing of 4 audio channels for sample rate conversion

- Flexible Signal Routing

- Each SRC module can independently select input sources

- Supports multiple operational mode combinations

- Freely configurable when no conflicts exist

- Dual SRC Module Architecture (SRC_A + SRC_B)

-

Ultra-High Sample Rate Conversion Support

- SSRC (Synchronous Sample Rate Conversion)

- Supports sample rate conversion between 44.1KHz-768KHz

- Ultra-high sampling rate support up to 768KHz

- ASRC (Asynchronous Sample Rate Conversion)

- Supports sample rate conversion between 44.1KHz-192KHz

- No external clock reference required

- Audio Data Processing

- Supports 16bit/24bit/32bit audio data processing

- High-precision digital signal processing

- SSRC (Synchronous Sample Rate Conversion)

-

Multiple Interface Support

- S/PDIF Interface

- 4 S/PDIF input interfaces (4-to-1 switching)

- 2 S/PDIF output interfaces (including loop-through output)

- Compatible with AES3, IEC 60958, and EIAJ CP-1201 standards

- Only supports 44.1KHz~192KHz (ASRC mode)

- I²S Interface

- 2 I²S interfaces (I²S_A and I²S_B)

- Supports Master/Slave mode (independently configurable)

- Flexible master/slave mode switching

- S/PDIF Interface

-

High Performance Specifications

-

Flexible Configuration Interface

- I²C/UART Configuration Interface

- Supports dual-protocol configuration via I²C and UART

- Configurable Parameters

- SRC module input source selection

- I²S sampling rate configuration

- Master/Slave mode switching

- S/PDIF input source switching (4-to-1)

- MCLK clock configuration (128fs/256fs/512fs/1024fs)

- I²C/UART Configuration Interface

-

Intelligent Clock Management

- Master Clock Output (MCLK_OUT)

- Supports 44.1KHz clock domain and 48KHz clock domain

- Clock Domain Restrictions

- Shared MCLK in dual I²S Master mode

- Must use the same clock domain (44.1KHz or 48KHz)

- Mute Indication

- Automatic mute during sampling rate switching

- Mute protection during configuration changes

- Master Clock Output (MCLK_OUT)

1.3 Application Scenarios¶

-

Professional Recording Studios

High-precision sample rate conversion requirements for multi-track recording equipment, audio workstations, and mixing console systems

-

Broadcasting and Television

Real-time audio signal processing in broadcasting equipment, television production, and live streaming systems

-

Digital Audio Systems

Signal optimization for amplifier equipment, audio processors, and speaker management systems

-

Automotive Audio

Audio processing for in-vehicle entertainment systems, premium audio systems, and noise reduction systems

-

Consumer Electronics

High-end audio equipment, home theater systems, and professional audio interface products

-

Industrial Applications

Test equipment, audio analysis instruments, and signal processing systems

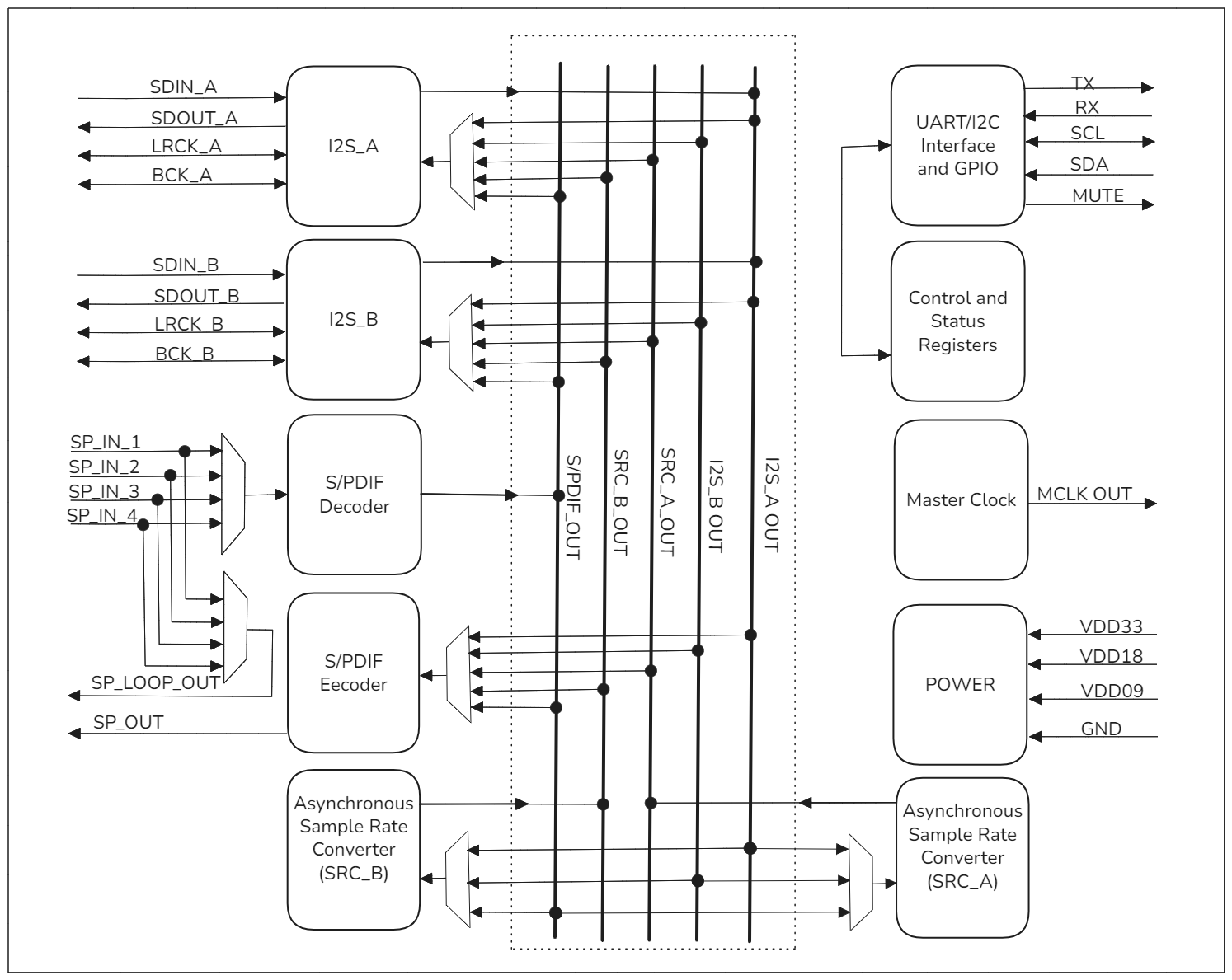

1.4 Product Block Diagram¶

1.5 Ordering Information¶

| PRODUCT MODEL | ORDERING NUMBER | PACKAGE BODY | SIZE (NOM) | Hardware Model | Comments |

|---|---|---|---|---|---|

| XMSRC4392-VC1 | XMSRC4392-VC1 | SMT LGA-52 | 13x13mm | A316-Mini-V1 | 4-channel sample rate converter, supports SSRC 768KHz/ASRC 192KHz, dual SRC modules with independent configuration |

2. Modes and Specifications¶

2.1 Supported Input/Output Modes¶

XMSRC4392-VC1 employs a flexible input/output routing architecture, supporting multiple audio processing modes. The following lists typical application modes from a data flow perspective:

| Mode | Input Interface | SRC Processing | Output Interface | Description |

|---|---|---|---|---|

| 1 | S/PDIF_IN | SRC_A + SRC_B | I²S_A_OUT + I²S_B_OUT | Single S/PDIF to I²S output |

| 2 | I²S_A_IN | SRC_A | I²S_A_OUT + I²S_B_OUT | Single input pass-through + converted dual output |

| 3 | I²S_A_IN + I²S_B_IN | SRC_A + SRC_B | I²S_A_OUT + I²S_B_OUT | Dual-channel cross sample rate conversion |

| 4 | S/PDIF_IN + I²S_B_IN | SRC_A + SRC_B | I²S_A_OUT + S/PDIF_OUT | S/PDIF and I²S bidirectional conversion |

| 5 | I²S_A_IN + I²S_B_IN | SRC_A | S/PDIF_OUT + I²S_B_OUT | I²S to S/PDIF, other channel pass-through |

Architecture Description

- Input Interfaces: S/PDIF_IN (4-to-1), I²S_A_DATA_IN, I²S_B_DATA_IN

- Output Interfaces: S/PDIF_OUT, I²S_A_DATA_OUT, I²S_B_DATA_OUT

- SRC Modules: 2 independent SRC modules (SRC_A, SRC_B), flexibly configurable for input sources and output destinations

- Pass-Through Mode: Data can pass directly from input to output without SRC processing (sample rate unchanged)

- I²S Interfaces: Each I²S interface is uniformly configured as Master or Slave; dual Master requires the same clock domain

2.2 Detailed Parameters for Each Operating Mode¶

2.2.1 Mode 1: Single S/PDIF to I²S Output¶

Application Scenario: Converting two S/PDIF signals to I²S output, suitable for digital audio systems

Data Flow:

| Channel | Input Interface | SRC Processing | Output Interface |

|---|---|---|---|

| Channel 1 | S/PDIF_IN (4-to-1) | SRC_A processing | I²S_A_DATA_OUT (Master) |

| Channel 2 | S/PDIF_IN (4-to-1) | SRC_B processing | I²S_B_DATA_OUT (Master) |

Signal Flow Diagram:

Parameter Description:

| Parameter | Channel 1 | Channel 2 |

|---|---|---|

| Input | S/PDIF_IN | S/PDIF_IN |

| SRC | SRC_A | SRC_B |

| Output | I²S_A_OUT (Master) | I²S_B_OUT (Master) |

| Sample Rate | 44.1KHz~192KHz (ASRC) | 44.1KHz~192KHz (ASRC) |

| Bit Depth | 16/24/32bit | 16/24/32bit |

Configuration Key Points

- Both I²S outputs operate in Master mode and must belong to the same clock family (44.1KHz series or 48KHz series)

2.2.2 Mode 2: Single I²S Input Dual Output (Pass-Through + Conversion)¶

Application Scenario: I²S_A input signal simultaneously passes through to output and is output from I²S_B after SRC conversion, suitable for scenarios where one source signal requires two different output sample rates

Data Flow:

| Data Path | Input Interface | SRC Processing | Output Interface |

|---|---|---|---|

| Path 1 | I²S_A_DATA_IN (Slave) | Without SRC (pass-through) | I²S_A_DATA_OUT (Slave) |

| Path 2 | I²S_A_DATA_IN (Slave) | SRC_A processing | I²S_B_DATA_OUT (Master) |

Signal Flow Diagram:

┌→ I²S_A_DATA_OUT (Slave, pass-through)

I²S_A_DATA_IN (Slave) ┤

└→ SRC_A ──→ I²S_B_DATA_OUT (Master)

Parameter Description:

| Parameter | Path 1 (Pass-Through) | Path 2 (Conversion) |

|---|---|---|

| Input | I²S_A_IN (Slave) | I²S_A_IN (Slave) |

| SRC | Not used (direct) | SRC_A |

| Output | I²S_A_OUT (Slave) | I²S_B_OUT (Master) |

| Sample Rate | Same as input (pass-through) | 44.1KHz~192KHz (ASRC) |

| Bit Depth | 16/24/32bit | 16/24/32bit |

Configuration Key Points

- I²S_A input is sent to two paths simultaneously: directly passed through to I²S_A output, and fed into SRC_A for processing

- Pass-through path does not change sample rate; conversion path can configure target sample rate

2.2.3 Mode 3: Dual I²S Input Cross Conversion Output¶

Application Scenario: Two I²S inputs are cross-output after SRC conversion, suitable for scenarios where dual audio channels need simultaneous conversion with swapped output interfaces

Data Flow:

| Channel | Input Interface | SRC Processing | Output Interface |

|---|---|---|---|

| Channel 1 | I²S_A_DATA_IN (Slave/Master) | SRC_A processing | I²S_B_DATA_OUT (Master/Slave) |

| Channel 2 | I²S_B_DATA_IN (Slave/Master) | SRC_B processing | I²S_A_DATA_OUT (Master/Slave) |

Signal Flow Diagram:

Parameter Description:

| Parameter | Channel 1 | Channel 2 |

|---|---|---|

| Input | I²S_A_IN (Slave/Master) | I²S_B_IN (Slave/Master) |

| SRC | SRC_A | SRC_B |

| Output | I²S_B_OUT (Master/Slave) | I²S_A_OUT (Master/Slave) |

| Sample Rate | 44.1KHz~192KHz (ASRC) 44.1KHz~768KHz (SSRC) | 44.1KHz~192KHz (ASRC) 44.1KHz~768KHz (SSRC) |

| Bit Depth | 16/24/32bit | 16/24/32bit |

Configuration Key Points

- Cross routing of two inputs: I²S_A input → SRC_A → I²S_B output, I²S_B input → SRC_B → I²S_A output

- Two SRC modules operate independently and can be set to different target sample rates

- SSRC requirement: Both I²S interfaces (input and output) must be configured in Master mode and must belong to the same clock family (44.1KHz series or 48KHz series)

2.2.4 Mode 4: S/PDIF and I²S Bidirectional Conversion¶

Application Scenario: S/PDIF input converts to I²S output while I²S input converts to S/PDIF output, suitable for digital audio format bidirectional conversion applications

Data Flow:

| Channel | Input Interface | SRC Processing | Output Interface |

|---|---|---|---|

| Channel 1 | S/PDIF_IN (4-to-1) | SRC_A processing | I²S_A_DATA_OUT (Master) |

| Channel 2 | I²S_B_DATA_IN (Slave) | SRC_B processing | S/PDIF_OUT |

Signal Flow Diagram:

S/PDIF_IN (4-to-1) ──→ SRC_A ──→ I²S_A_DATA_OUT (Master)

I²S_B_DATA_IN (Slave) ──→ SRC_B ──→ S/PDIF_OUT

Parameter Description:

| Parameter | Channel 1 | Channel 2 |

|---|---|---|

| Input | S/PDIF_IN | I²S_B_IN (Slave) |

| SRC | SRC_A | SRC_B |

| Output | I²S_A_OUT (Master) | S/PDIF_OUT |

| Sample Rate | 44.1KHz~192KHz (ASRC) | 44.1KHz~192KHz (ASRC) |

| Bit Depth | 16/24/32bit | 16/24/32bit |

Configuration Key Points

- Implements bidirectional conversion between S/PDIF and I²S formats

2.2.5 Mode 5: I²S to S/PDIF Output + Other I²S Pass-Through¶

Application Scenario: I²S_A input converts to S/PDIF output, I²S_B independently passes through, suitable for applications where one channel requires format conversion and the other passes directly

Data Flow:

| Channel | Input Interface | SRC Processing | Output Interface |

|---|---|---|---|

| Channel 1 | I²S_A_DATA_IN (Slave) | SRC_A processing | S/PDIF_OUT |

| Channel 2 | I²S_B_DATA_IN (Master) | Without SRC (pass-through) | I²S_B_DATA_OUT (Master) |

Signal Flow Diagram:

I²S_A_DATA_IN (Slave) ──→ SRC_A ──→ S/PDIF_OUT

I²S_B_DATA_IN (Master) ──→ I²S_B_DATA_OUT (Master, pass-through)

Parameter Description:

| Parameter | Channel 1 (Conversion) | Channel 2 (Pass-Through) |

|---|---|---|

| Input | I²S_A_IN (Slave) | I²S_B_IN (Master) |

| SRC | SRC_A | Not used (direct) |

| Output | S/PDIF_OUT | I²S_B_OUT (Master) |

| Sample Rate | 44.1KHz~192KHz (ASRC) | Same as input (pass-through) |

| Bit Depth | 16/24/32bit | 16/24/32bit |

Configuration Key Points

- I²S_B input passes directly to output without SRC processing, sample rate unchanged

2.3 Audio Performance Specifications¶

| Performance Specification | SSRC Mode | ASRC Mode | Notes |

|---|---|---|---|

| THD+N | ≤ -130dB | ≤ -130dB | @1kHz, 0dBFs |

| Sample Rate Range | 44.1KHz~768KHz | 44.1KHz~192KHz | - |

| Audio Resolution | 16/24/32bit | 16/24/32bit | - |

| SRC Channels | 4 channels | 4 channels | 2 channels per dual module |

| SRC Modules | 2 independent modules | 2 independent modules | SRC_A + SRC_B |

SSRC Mode Limitations

SSRC Mode Usage Conditions:

- Input and output interfaces must be I²S Master

- Multiple I²S Masters must operate in the same clock domain (all in 44.1KHz series or all in 48KHz series)

If the above conditions are not met, only ASRC mode can be used (sample rate limited to 44.1KHz~192KHz)

2.4 Feature Comparison¶

| Feature | XMSRC4392 | SRC4392 | Advantage |

|---|---|---|---|

| SRC Channels | 4 channels | 2 channels | 2x processing capability |

| SRC Modules | 2 independent modules | 1 module | 2x processing capability |

| Maximum Sample Rate (SSRC) | 768 KHz | 216 KHz | 3.5x performance improvement |

| Maximum Sample Rate (ASRC) | 192 KHz | 216 KHz | Equivalent performance |

| External Clock Reference | No external clock required | Requires external clock | Saves external crystal cost |

| Scalability | Expandable | Not expandable | More flexible |

3. Pin Configuration and Functions¶

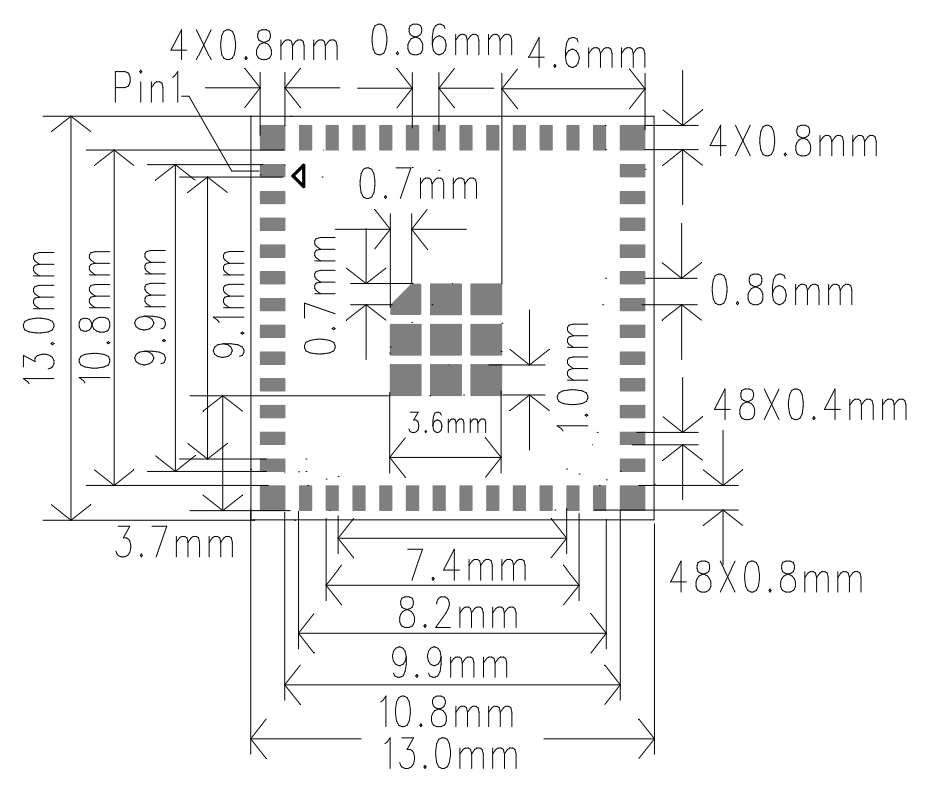

3.1 XMSRC4392_VC1 Pin Layout¶

3.2 XMSRC4392_VC1 Pin Description¶

| Pin Number | Name | Type | Function |

|---|---|---|---|

| 1 | 3.3V | P | Module 3.3V power supply |

| 2 | X1D13 | - | Reserved |

| 3 | X1D16 | - | Reserved |

| 4 | GND | P | Module ground |

| 5 | X1D17 | - | Reserved |

| 6 | X1D18 | - | Reserved |

| 7 | X1D19 | - | Reserved |

| 8 | X1D22 | O | SP_OUT (S/PDIF output, source selectable from SRC_A or SRC_B) |

| 9 | X0D29 | I/O | UART_RX/I2C_SDA (UART receive/I2C data) |

| 10 | X0D35 | I/O | BCK_A (I²S_A bit clock, Master output/Slave input) |

| 11 | X0D36 | I/O | LRCK_A (I²S_A frame sync, Master output/Slave input) |

| 12 | X0D37 | I/O | SDIN_A (I²S_A data input) |

| 13 | X0D38 | O | SDOUT_A (I²S_A data output) |

| 14 | X0D40 | I | SP_IN_2 (S/PDIF input 2) |

| 15 | X0D39 | O | MCLK (Master clock output, Master mode) |

| 16 | X0D42 | I | SP_IN_4 (S/PDIF input 4) |

| 17 | X0D41 | I | SP_IN_3 (S/PDIF input 3) |

| 18 | X0D43 | - | Reserved |

| 19 | X1D34 | I/O | SDIN_B (I²S_B data input) |

| 20 | GND | P | Module ground |

| 21 | X0D30 | I/O | I2C_SCL (I2C clock) |

| 22 | X0D31 | I/O | UART_I2C_SEL (UART/I2C selection) |

| 23 | X0D32 | I/O | UART_TX (UART transmit) |

| 24 | X0D33 | O | MUTE (Mute indication output) |

| 25 | GND | P | Module ground |

| 26 | GND | P | Module ground |

| 27 | GND | P | Module ground |

| 28 | X0D00 | O | SP_LOOP_OUT (S/PDIF loop-through output, direct pass-through of selected input) |

| 29 | X0D11 | I | SP_IN_1 (S/PDIF input 1) |

| 30 | X1D00 | I/O | LRCK_B (I²S_B frame sync, Master output/Slave input) |

| 31 | X1D01 | O | SDOUT_B (I²S_B data output) |

| 32 | GND | P | Module ground |

| 33 | X1D09 | - | Reserved |

| 34 | X1D10 | I/O | BCK_B (I²S_B bit clock, Master output/Slave input) |

| 35 | X1D11 | O | MCLK (Master clock output) |

| 36 | GND | P | Module ground |

| 37 | GND | P | Module ground |

| 38 | TDI | I/O | XTAG debug pin |

| 39 | TDO | I/O | XTAG debug pin |

| 40 | TMS | I/O | XTAG debug pin |

| 41 | TCK | I/O | XTAG debug pin |

| 42 | RST_N | I | System reset, active low |

| 43 | 1.8V | P | Module 1.8V power supply |

| 44 | GND | P | Module ground |

| 45 | USB_DM | I/O | USB_DM (Reserved, not used) |

| 46 | USB_DP | I/O | USB_DP (Reserved, not used) |

| 47 | GND | P | Module ground |

| 48 | 0.9V | P | Module 0.9V power supply |

| 49 | GND | P | Module ground |

| 50 | GND | P | Module ground |

| 51 | GND | P | Module ground |

| 52 | GND | P | Module ground |

Pin Type Description

Pin types in table: I=Input, O=Output, P=Power, I/O=Input/Output

Important Notes

- S/PDIF Inputs: 4 inputs (SP_IN_1~SP_IN_4) switchable via 4-to-1 configuration

- Pin 29 (X0D11): SP_IN_1

- Pin 14 (X0D40): SP_IN_2

- Pin 17 (X0D41): SP_IN_3

- Pin 16 (X0D42): SP_IN_4

- SP_LOOP_OUT: Pin 28 (X0D00), directly loops back the selected S/PDIF input without SRC processing

- S/PDIF Output: Pin 8 (X1D22), configurable to select SRC_A or SRC_B output (choose one)

- UART/I2C Interface Selection: Interface type selected via pin 22 (X0D31) UART_I2C_SEL signal

- UART mode: Pin 9 (X0D29) = UART_RX, Pin 23 (X0D32) = UART_TX

- I2C mode: Pin 9 (X0D29) = I2C_SDA, Pin 21 (X0D30) = I2C_SCL

- MCLK Output: Pin 15 (X0D39) and Pin 35 (X1D11)

- Frequency: 128fs/256fs/512fs/1024fs

- Dual Master Limitation: When both I²S_A and I²S_B are in Master mode, they must use the same clock domain

- MUTE Signal: Pin 24 (X0D33), outputs mute indication during sample rate or configuration switching

4. Configuration Interface Description¶

4.1 I²C/UART Configuration Interface¶

XMSRC4392-VC1 supports both I²C and UART dual-protocol configuration, providing flexible configuration methods. The configuration interface type can be selected via pin 22 (X0D31) UART_I2C_SEL signal: | Configuration Method | Pin 22 (X0D31) | Communication Interface | Description | |:--------|:-------------|:---------|:-----| | Pull-up | UART_I2C_SEL | UART mode | Pin 9 (X0D29) = UART_RX, Pin 23 (X0D32) = UART_TX | | Pull-down | UART_I2C_SEL | I²C mode | Pin 9 (X0D29) = I2C_SDA, Pin 21 (X0D30) = I2C_SCL |

4.2 Configurable Parameters¶

The following parameters can be configured via I²C or UART interface:

| Parameter Type | Configuration Options | Description |

|---|---|---|

| SRC_A Input Source | S/PDIF_IN / I²S_A_IN / I²S_B_IN | Select input source for SRC_A module |

| SRC_B Input Source | S/PDIF_IN / I²S_A_IN / I²S_B_IN | Select input source for SRC_B module |

| S/PDIF Input Selection | SP_IN_1 / SP_IN_2 / SP_IN_3 / SP_IN_4 | 4-to-1 switching |

| I²S_A Mode | Master / Slave | I²S_A operating mode |

| I²S_B Mode | Master / Slave | I²S_B operating mode |

| I²S_A Sample Rate | 44.1KHz~768KHz | Configuration in Master mode |

| I²S_B Sample Rate | 44.1KHz~768KHz | Configuration in Master mode |

| MCLK Clock Configuration | 128fs/256fs/512fs/1024fs | MCLK output multiplier selection |

Configuration Notes

- Configuration switching triggers the MUTE signal

- In dual Master mode, the same clock domain must be configured (44.1KHz or 48KHz)

- Refer to configuration protocol documentation for detailed configuration commands

4.3 MCLK Output Frequency Configuration¶

MCLK_OUT frequency is determined by the clock domain and configured multiplier (128fs/256fs/512fs/1024fs).

| Clock Domain | MCLK Configuration | Output Frequency Examples |

|---|---|---|

| 44.1KHz | 128fs/256fs/512fs/1024fs | 5.6448MHz ~ 45.158MHz |

| 48KHz | 128fs/256fs/512fs/1024fs | 6.144MHz ~ 49.152MHz |

Clock Domain Restrictions

When both I²S_A and I²S_B operate in Master mode:

- ✅ Allowed: Both in 44.1KHz domain OR both in 48KHz domain

- ❌ Not Allowed: One in 44.1KHz domain, the other in 48KHz domain

5. Hardware Parameters¶

5.1 Normal Operating Conditions¶

| Function | Minimum | Typical | Maximum | Unit |

|---|---|---|---|---|

| Operating Temperature | 0 | - | 70 | ℃ |

| 3.3V Operating Voltage | 3.0 | 3.3 | 3.6 | V |

| 1.8V Operating Voltage | 1.62 | 1.80 | 1.98 | V |

| 0.9V Operating Voltage | 0.855 | 0.90 | 0.945 | V |

5.2 Product Dimensions¶

13±0.1mm(L)X13±0.1mm(W)X0.8±0.1mm(H)

5.3 Module Package Diagram¶

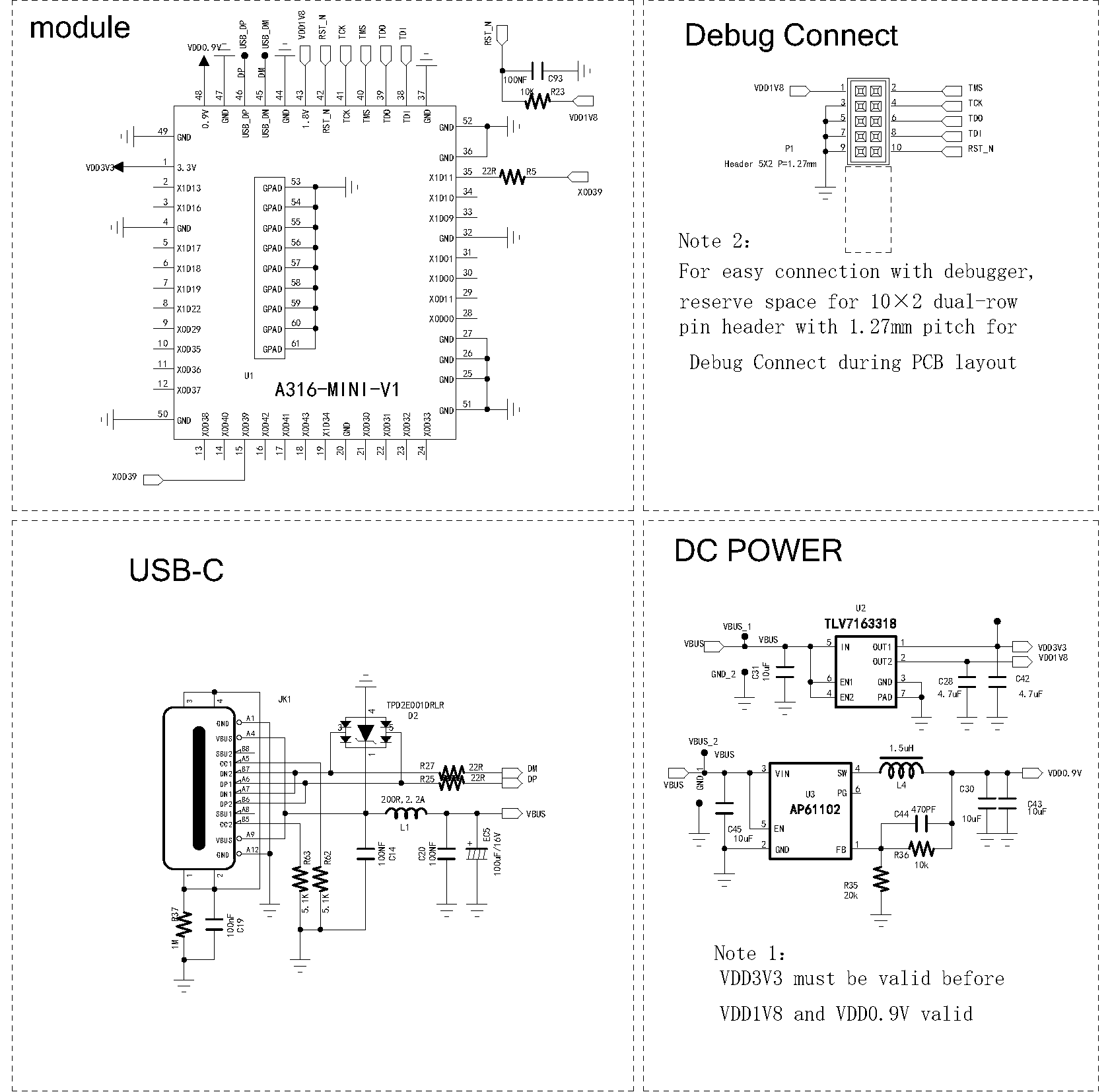

6. Minimum System Reference Design¶

7. Product Packaging Information¶

Tray + Outer Box Packaging

8. Revision History¶

| Version | Date | Description | Author |

|---|---|---|---|

| V1.0 | 2025-10-5 | Initial version release | |