HF86611_VC1/HF86611Q_VC1¶

Multi-Channel PCM 768kHz/DSD512 USB HiFi Decoder Supporting USB/4-Channel SPDIF Input and I2S Output

1. Introduction¶

1.1 Product Description¶

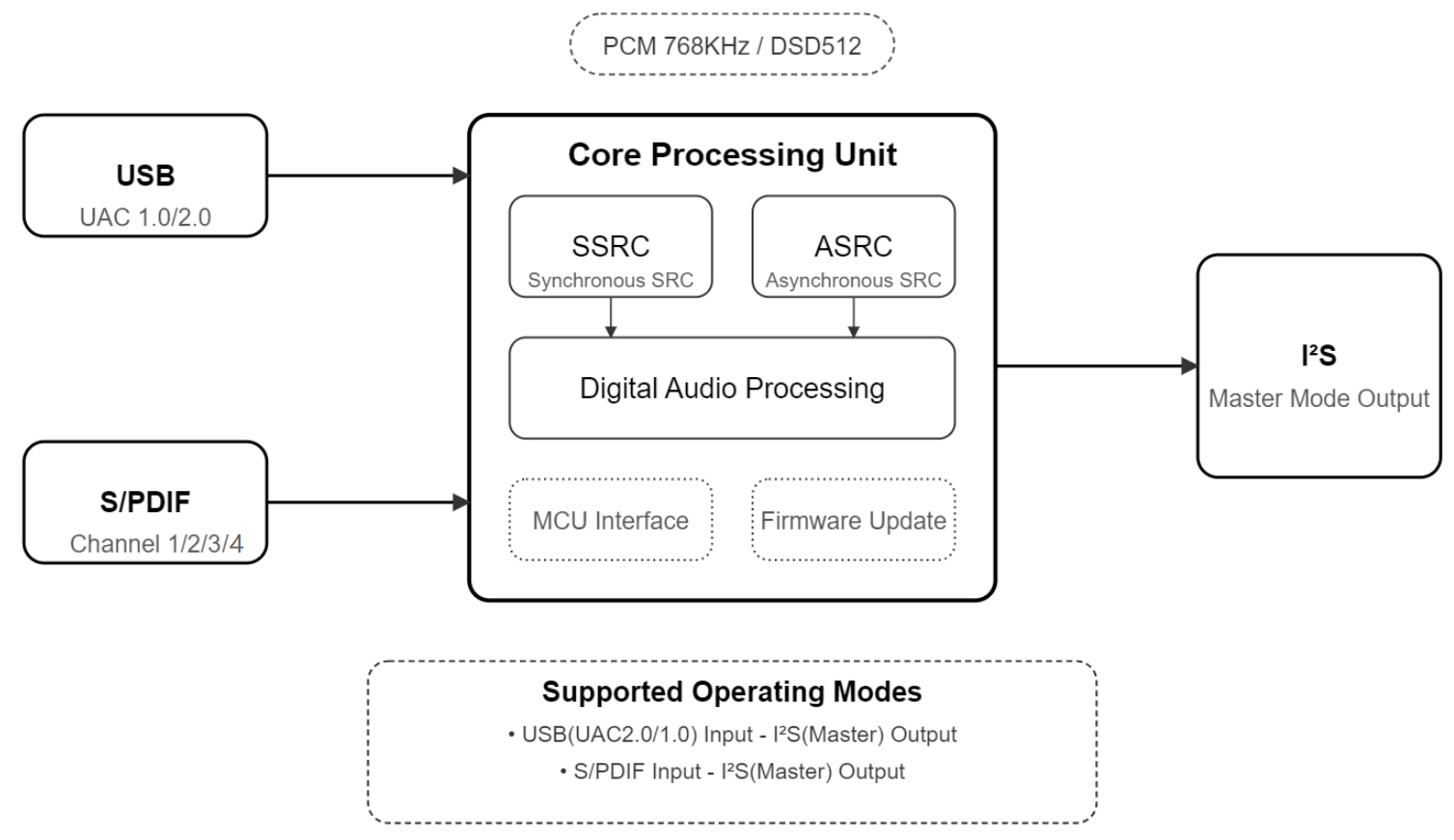

HF86611_VC1/HF86611Q_VC1 is a USB multi-channel and multi-interface HiFi audio decoder that supports up to PCM 768kHz/DSD512, designed specifically for HiFi audio DAC applications.

HF86611_VC1/HF86611Q_VC1 supports multiple standard audio formats, including USB Audio Class 1.0/2.0, S/PDIF and I²S interfaces. The flexible audio interfaces allow HF86611_VC1/HF86611Q_VC1 to connect to various audio data converters, digital audio receivers and transmitters, as well as digital signal processors.

It is compatible with AES3, S/PDIF, IEC 60958, and EIAJ CP-1201 digital audio interfaces.

HF86611_VC1/HF86611Q_VC1 provides multiple input and output modes, including USB input/I²S output and S/PDIF input/I²S output, to meet the requirements of different application scenarios.

Important Note

Model HF86611Q_VC1 supports MQA audio decoding, while model HF86611_VC1 does not support this feature.

1.2 Product Features¶

Audio Performance Features

- Supports input and output sample rates up to 768kHz

- Supports DSD64/128/256/512 formats

- HF86611Q_VC1 supports MQA decoding

- Built-in SSRC and ASRC modules, supporting sample rate conversion between different interfaces and different sample rates

- Supports 16–32-bit audio data formats

- Supports four S/PDIF input channels

Interface Support Features

- Multiple digital interface support

- Supports USB audio input

- Supports I²S master mode audio output

- Supports S/PDIF audio input

- Supports UART configuration interface

USB Function Features

- USB interface features

- Supports UAC 1.0

- Supports UAC 2.0

- Supports firmware upgrade via USB

- Supports HID and can upgrade MCU firmware via HID

System Compatibility

- UAC 2.0 protocol, supports ASIO

- Supports multiple operating systems, such as Windows, Linux, Android, macOS and iOS

1.3 Application Scenarios¶

- USB HiFi Decoder

- USB HiFi Audio Interface

- USB HiFi Digital Player

1.4 Product Functional Block Diagram¶

1.5 Ordering Information¶

| PRODUCT | ORDERING NUMBER | PACKAGE BODY | SIZE (NOM) | Hardware Model | Comments |

|---|---|---|---|---|---|

| HF86611_VC1 | HF86611-VC1 | SMT LGA-52 | 13x13mm | A316-Mini-V1 | |

| HF86611Q_VC1 | HF86611Q-VC1 | SMT LGA-52 | 13x13mm | A316-Mini-V1 | Supports MQA decoding |

2. Modes and Specifications¶

2.1 Supported Input/Output Modes¶

| Mode No. | Input/Output Mode | Description |

|---|---|---|

| 1 | USB(UAC2.0) in-I²S(MASTER) out | USB input, I²S output, UAC2.0 |

| 2 | USB(UAC1.0) in-I²S(MASTER) out | USB input, I²S output, UAC1.0 |

| 3 | S/PDIF1 IN-I²S(MASTER) OUT | S/PDIF channel 1 input, I²S output |

| 4 | S/PDIF2 IN-I²S(MASTER) OUT | S/PDIF channel 2 input, I²S output |

| 5 | S/PDIF3 IN-I²S(MASTER) OUT | S/PDIF channel 3 input, I²S output |

| 6 | S/PDIF4 IN-I²S(MASTER) OUT | S/PDIF channel 4 input, I²S output |

2.2 Detailed Parameters of Each Operating Mode¶

2.2.1 USB(UAC2.0) in → I²S out Mode¶

Supported Audio Formats and Sample Rates:

| Audio Format | Supported Sample Rates |

|---|---|

| PCM | 44.1kHz, 48kHz, 88.2kHz, 96kHz, 176.4kHz, 192kHz, 352.8kHz, 384kHz, 705.6kHz, 768kHz |

| DSD Native | DSD64, DSD128, DSD256, DSD512 |

| DOP | DOP64, DOP128, DOP256 |

| MQA | Supported only by HF86611Q_VC1 |

2.2.2 USB(UAC1.0) in → I²S out Mode¶

Supported Audio Formats and Sample Rates:

| Audio Format | Supported Sample Rates |

|---|---|

| PCM | 48kHz |

2.2.3 S/PDIF in → I²S out Mode¶

Supported Audio Formats and Sample Rates:

| Audio Format | Supported Sample Rates |

|---|---|

| PCM | 44.1kHz, 48kHz, 88.2kHz, 96kHz, 176.4kHz, 192kHz |

3. Pin Configuration and Functions¶

3.1 HF86611_VC1/HF86611Q_VC1 Pin Layout¶

3.2 HF86611_VC1/HF86611Q_VC1 Pin Description¶

| Pin No. | Name | Type | Function |

|---|---|---|---|

| 1 | 3.3V | P | Module 3.3V power supply |

| 2 | X1D13 | I/O | S/PDIF channel 1 input |

| 3 | X1D16 | I/O | NC |

| 4 | GND | P | Module ground |

| 5 | X1D17 | I/O | NC |

| 6 | X1D18 | I/O | NC |

| 7 | X1D19 | I/O | NC |

| 8 | X1D22 | I/O | S/PDIF channel 2 input |

| 9 | X0D29 | I/O | NC |

| 10 | X0D35 | I/O | I²S_OUT_BCLK(MASTER) |

| 11 | X0D36 | I/O | I²S_OUT_LRCLK(MASTER) |

| 12 | X0D37 | I/O | NC |

| 13 | X0D38 | I/O | I²S_OUT_DATA0(MASTER) |

| 14 | X0D40 | I/O | NC |

| 15 | X0D39 | I/O | I²S_OUT_MCLK(MASTER) |

| 16 | X0D42 | I/O | NC |

| 17 | X0D41 | I/O | NC |

| 18 | X0D43 | I/O | NC |

| 19 | X1D34 | I/O | S/PDIF channel 3 input |

| 20 | GND | P | Module ground |

| 21 | X0D30 | I/O | CTL_MUTE; control output, active high |

| 22 | X0D31 | I/O | NC |

| 23 | X0D32 | I/O | NC |

| 24 | X0D33 | I/O | NC |

| 25 | GND | P | Module ground |

| 26 | GND | P | Module ground |

| 27 | GND | P | Module ground |

| 28 | X0D00 | I/O | UART_TX, connected to MCU_RX |

| 29 | X0D11 | I/O | UART_RX, connected to MCU_TX |

| 30 | X1D00 | I/O | NC |

| 31 | X1D10 | I/O | NC |

| 32 | GND | P | Module ground |

| 33 | X1D09 | I/O | NC |

| 34 | X1D01 | I/O | S/PDIF channel 4 input |

| 35 | X1D11 | I/O | Connected to Pin 15 X0D39 |

| 36 | GND | P | Module ground |

| 37 | GND | P | Module ground |

| 38 | TDI | I/O | XTAG debug pin |

| 39 | TDO | I/O | XTAG debug pin |

| 40 | TMS | I/O | XTAG debug pin |

| 41 | TCK | I/O | XTAG debug pin |

| 42 | RST_N | I/O | System reset, active low |

| 43 | 1.8V | P | Module 1.8V power supply |

| 44 | GND | P | Module ground |

| 45 | USB_DM | I/O | USB_DM |

| 46 | USB_DP | I/O | USB_DP |

| 47 | GND | P | Module ground |

| 48 | 0.9V | P | Module 0.9V power supply |

| 49 | GND | P | Module ground |

| 50 | GND | P | Module ground |

| 51 | GND | P | Module ground |

| 52 | GND | P | Module ground |

Pin Type Description

In the table, I/O type definitions: I = input, O = output, P = power, I/O = input/output

4. Revision History¶

| Version | Date | Description | Editor |

|---|---|---|---|

| V1.0 | 2025-05-07 | Initial version release | |